EE7.9 Library Manager. Создание ячеек. Ячейка SO-8

Мои статьи

Предыдущая статья

В этой и следующей статье я расскажу как в программе Cell Editor создаются посадочные места для микросхем поверхностного монтажа.

Прежде всего, для создания ячеек, должны быть созданы падстеки, об их создании я писал в предыдущих статьях.

А сейчас, если библиотека electronic-labs.lmc еще не открыта в программе Library Manager, то откроем её.

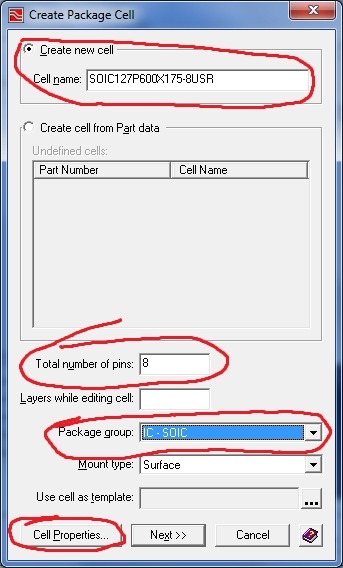

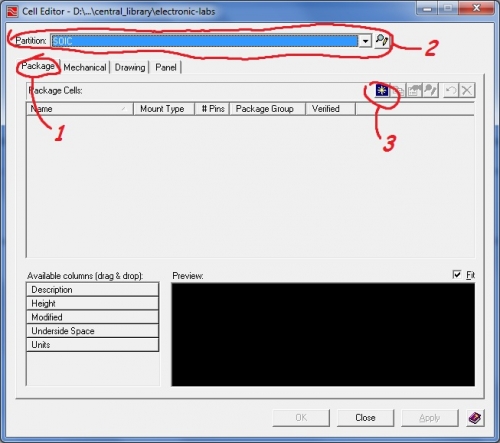

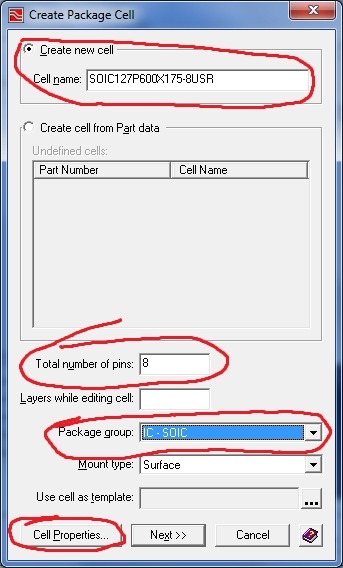

Запустится новое окно, в нем выбираем опцию Create new cell и вводим название ячейки. В нашем случае: SOIC127P600X175-8USR. В поле Total number of pins вводим 8. В качестве Package group выбираем из выпадающего списка IC-SOIC

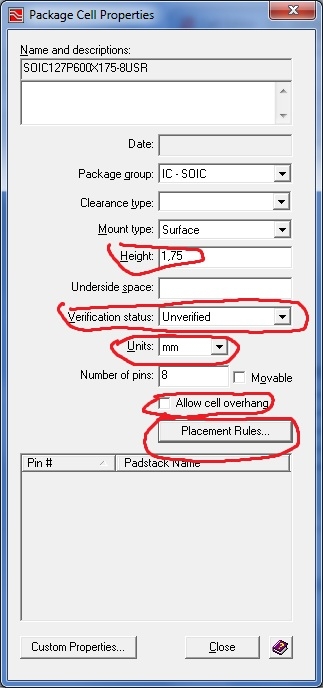

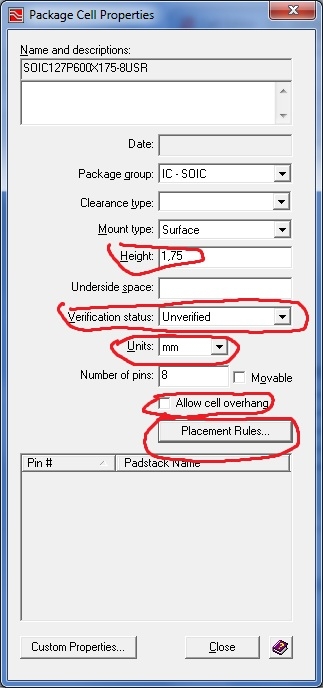

Нажимаем клавишу Cell Properties. В появившемся окне в качестве высоты вводим 1,75. Убеждаемся, что в качестве единиц измерения выбраны миллиметры, статус ячейки Unverified, что означает, что ячейка пока не прошла проверку, а галочка allow cell overhang — снята. Эта галочка должна быть установлена только для компонентов, которые могут выходить за границу платы (разъемы, устройства извлечения карт и т.п.). В окне Package Cell Properties нажимаем Placement Rules

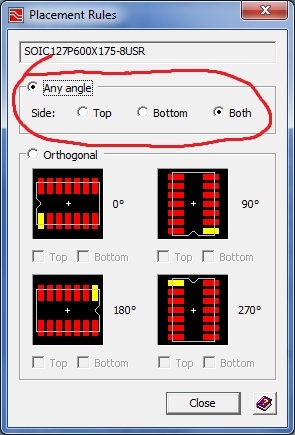

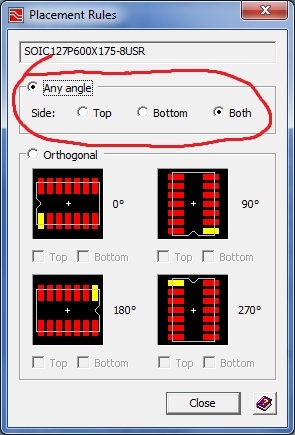

В этом окне ничего менять не нужно. Просто для ознакомления смотрим, что размещать можем на любом слое и под любым углом. На самом же деле можно настроить определенные направления на верхнем и нижнем слоях, что может быть полезно, например, при пайке волной припоя.

Закрываем поочередно окна Placement Rules, Package Cell Properties, и нажимаем Next в окне Create Package Cell

На этом подготовительный этап закончен, и начинается, собственно, создание ячейки.

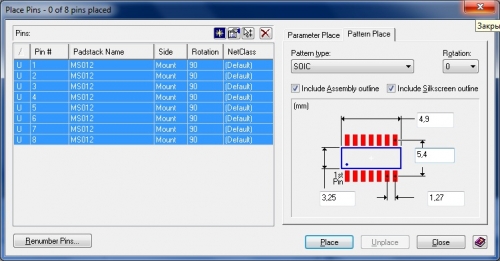

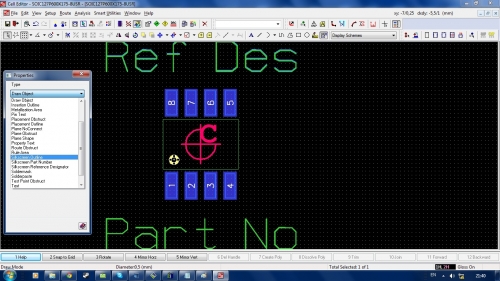

Надо всё сделать, как на этом рисунке:

Есть несколько хитростей, как сделать это проще. Кликаем в любом столбце в первой строчке, зажимаем шифт, и кликаем в любом столбце последней строчки, так должны выбраться все выводы. После чего, не отпуская Shift, в столбце Padstack Name в последней строчке выбираем нужный нам падстек. В данном случае — MS012 — и он должен установиться сразу для всех выводов. После этого, удерживая Shift, выбираем угол поворота 90 градусов.

Далее, в правой части экрана выбираем вкладку Pattern Place, выбираем SOIC в качестве Pattern type, оставляем галочки установленными.

После этого вводим необходимые размеры: шелкографию 4.9X3.25, расстояние между соседними выводами 1.27, а между противоположными — 5.4 мм. После чего можно нажать клавишу Place

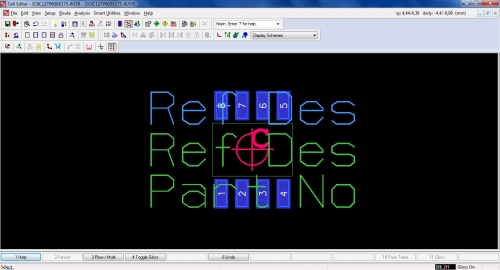

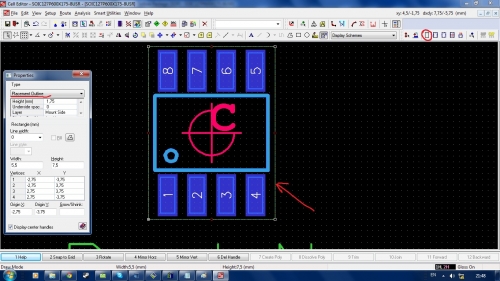

Должно появится нечто вроде вот этого:

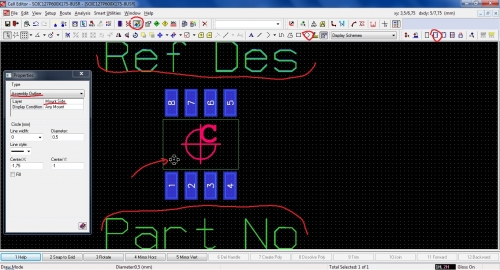

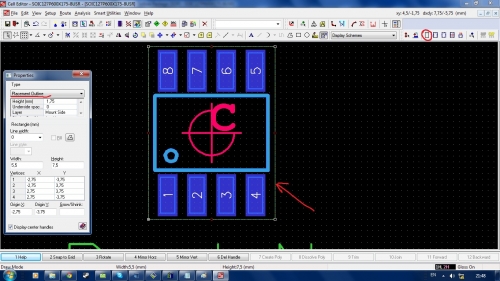

После чего, создать круг, показывающий первый вывод, для чего, можно нажать на кнопку Place Assembly Outline и нарисовать окружность.

Теперь нужно создать шелкографию. Это крайне просто:

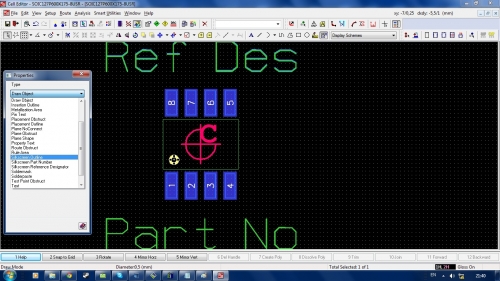

Выбираем графику на слое Assembly, на картинке показан трюк с окружностью. При выбранном элементе, дежрим Crtl и дважды кликаем на элемент. Появляется его копия типа Draw Object, теперь вместо Draw Object надо только выбрать Silkscreen Outline и установить толщину линии в 0,15мм. Ну и повторить трюк со всеми объектами, которые хотим скопировать.

И добавляем courtyard.

Теперь можно сохранить элемент и выбрать File->Exit Graphics.

Выйдем из программы Cell Editor, и снова зайдем в ней, после чего выберем раздел SOIC. Заметьте, что наша вновь созданная ячейка выделена цветом — это потому что она неверифицирована — можно исправить это, если хочется… и уж абсолютно точно нужно, чтобы работать с этой ячейкой при проектировании плат.

Предыдущая статья

В этой и следующей статье я расскажу как в программе Cell Editor создаются посадочные места для микросхем поверхностного монтажа.

Прежде всего, для создания ячеек, должны быть созданы падстеки, об их создании я писал в предыдущих статьях.

А сейчас, если библиотека electronic-labs.lmc еще не открыта в программе Library Manager, то откроем её.

Создание ячейки SO8

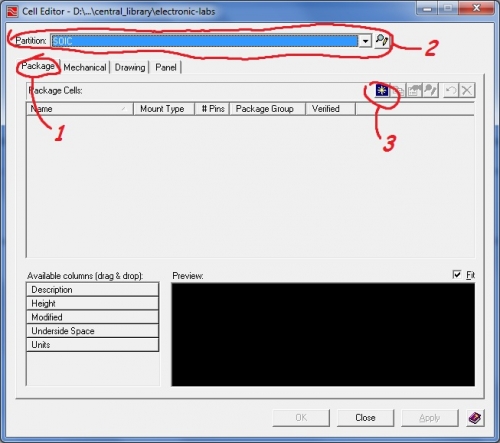

запустим утилиту Cell Editor: Tools->Cell Editor. В открывшемся окне Выбираем вкладку Package, в качестве Partition выбираем SOIC. Нажимаем кнопку создания новой ячейки. Все примерно вот так:

Запустится новое окно, в нем выбираем опцию Create new cell и вводим название ячейки. В нашем случае: SOIC127P600X175-8USR. В поле Total number of pins вводим 8. В качестве Package group выбираем из выпадающего списка IC-SOIC

Нажимаем клавишу Cell Properties. В появившемся окне в качестве высоты вводим 1,75. Убеждаемся, что в качестве единиц измерения выбраны миллиметры, статус ячейки Unverified, что означает, что ячейка пока не прошла проверку, а галочка allow cell overhang — снята. Эта галочка должна быть установлена только для компонентов, которые могут выходить за границу платы (разъемы, устройства извлечения карт и т.п.). В окне Package Cell Properties нажимаем Placement Rules

В этом окне ничего менять не нужно. Просто для ознакомления смотрим, что размещать можем на любом слое и под любым углом. На самом же деле можно настроить определенные направления на верхнем и нижнем слоях, что может быть полезно, например, при пайке волной припоя.

Закрываем поочередно окна Placement Rules, Package Cell Properties, и нажимаем Next в окне Create Package Cell

На этом подготовительный этап закончен, и начинается, собственно, создание ячейки.

Расположение контактных площадок

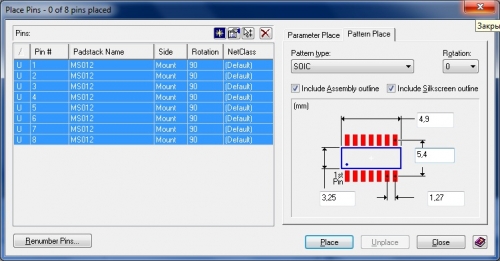

Собственно, после предыдущего шага у нас должно появиться окно Place Pins.Надо всё сделать, как на этом рисунке:

Есть несколько хитростей, как сделать это проще. Кликаем в любом столбце в первой строчке, зажимаем шифт, и кликаем в любом столбце последней строчки, так должны выбраться все выводы. После чего, не отпуская Shift, в столбце Padstack Name в последней строчке выбираем нужный нам падстек. В данном случае — MS012 — и он должен установиться сразу для всех выводов. После этого, удерживая Shift, выбираем угол поворота 90 градусов.

Далее, в правой части экрана выбираем вкладку Pattern Place, выбираем SOIC в качестве Pattern type, оставляем галочки установленными.

После этого вводим необходимые размеры: шелкографию 4.9X3.25, расстояние между соседними выводами 1.27, а между противоположными — 5.4 мм. После чего можно нажать клавишу Place

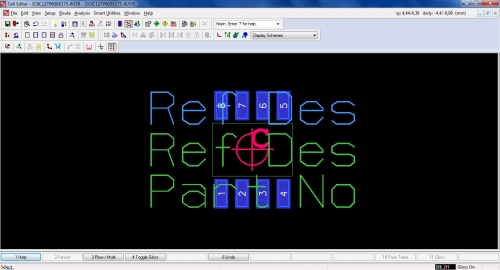

Должно появится нечто вроде вот этого:

Создание графики компонента

Сейчас нам нужно перейти в режим Draw Mode и разместить оба Ref Des над графикой микросхемы, а Parn No — под графикой.После чего, создать круг, показывающий первый вывод, для чего, можно нажать на кнопку Place Assembly Outline и нарисовать окружность.

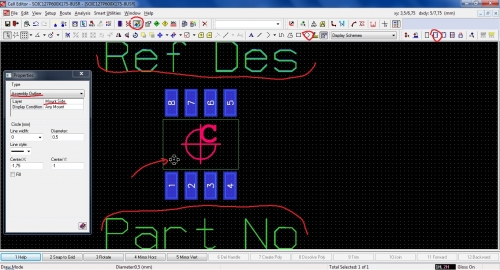

Теперь нужно создать шелкографию. Это крайне просто:

Выбираем графику на слое Assembly, на картинке показан трюк с окружностью. При выбранном элементе, дежрим Crtl и дважды кликаем на элемент. Появляется его копия типа Draw Object, теперь вместо Draw Object надо только выбрать Silkscreen Outline и установить толщину линии в 0,15мм. Ну и повторить трюк со всеми объектами, которые хотим скопировать.

И добавляем courtyard.

Теперь можно сохранить элемент и выбрать File->Exit Graphics.

Выйдем из программы Cell Editor, и снова зайдем в ней, после чего выберем раздел SOIC. Заметьте, что наша вновь созданная ячейка выделена цветом — это потому что она неверифицирована — можно исправить это, если хочется… и уж абсолютно точно нужно, чтобы работать с этой ячейкой при проектировании плат.

9 комментариев